JTAG timing specification

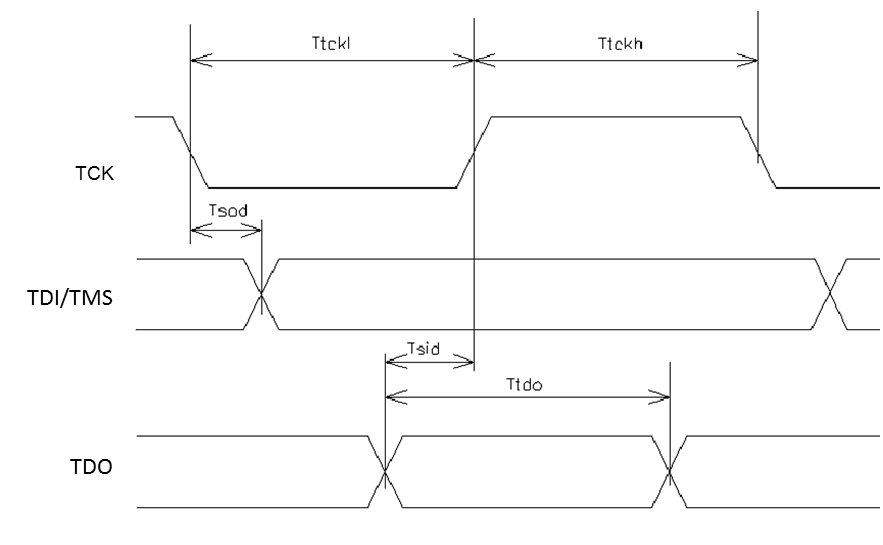

This figure shows the JTAG timing and parameters:

In a JTAG device that fully complies to IEEE1149.1 standard, the TDI/TMS signals should be sampled on the rising edge of TCK, and TDO should be sent on the falling edge of TCK. I-jet takes advantage of these requirements and changes its TDI and TMS signals on the falling edge of TCK and samples the TDO on the rising edge of TCK. However, to accommodate target boards with long JTAG chains and fast JTAG clocks, I-jet allows TDO to be as late as 50 ns after the rising edge of TCK.

IAR Embedded Workbench for Arm: In the adaptive mode of operation, I-jet samples the TDO on the rising edge of RTCK rather than TCK.

This table shows the timing specifications of the JTAG port measured at the end of its MIPI-20 cable without connection to target (VTref set to 3.3 V). The only load on the measured signals is the oscilloscope 3.9 pF probe.

Parameter | Min | Max | Description |

|---|---|---|---|

Ttckl | 15.6 ns | 250 us | TCK LOW period |

Ttckh | 15.6 ns | 250 us | TCK HIGH period |

Tsod1 | — | 2.0 ns | TDI and TMS outputs valid from TCK falling |

Tsid2 | 3 ns before TCK to 50 ns after TCK | — | TDO setup to TCK rising |

Ttdo | Ttckl | — | TDO valid length |

1 Tsod is the maximum delay from the falling edge of TCK and a valid level on the I-jet output signals, TDI and TMS. The target MCU will sample these signals on the following rising edge of TCK and so the minimum setup time for the target, relative to the rising edge of TCK, is Ttckl–Tsod.

2 Tsid is the minimum setup time for the TDO input signal, relative to the rising edge of TCK when I-jet samples this signal. Because the target MCU changes its TDO value on the previous falling edge of TCK, there might not be enough time at very-high JTAG speeds for the TDO to arrive before the positive edge of TCK. To compensate for any TDO delays, I-jet configures itself automatically to delays introduced to the TDO by the target board and will tolerate TDO delays of up to 50 ns after the positive edge of the TCK.