Multicore RH850 microcontrollers

RH850 is a symmetric multi-core (SMP) microcontroller, which means that there are two or more identical CPUs on the same physical integrated circuit.

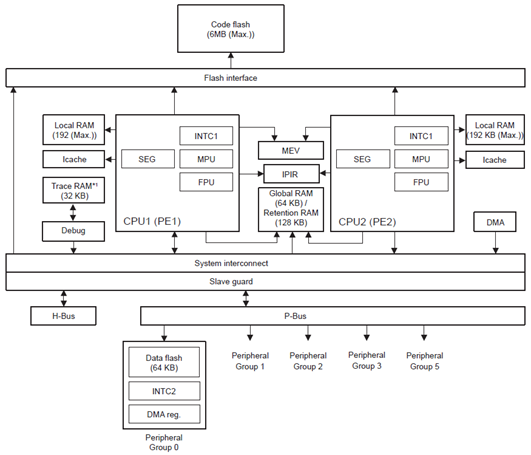

This figure describes RH850/F1H, which is a dual core MCU.

Each CPU has a high-speed accessible Local RAM. In addition, there is a common Global RAM for data sharing among the CPUs. A part of the global RAM area works as a retention RAM, which means that the content is kept as long the power supply voltage is sufficient. The code flash memory is used as application storage. All cores share the code flash via an interface. The data flash is a shared rewritable flash memory that supports more rewrites than the code flash memory.

On a dual-core microcontroller, two applications can be executed independently by separate cores without interfering with each other. If data needs to be passed between the applications, both cores have access to the global RAM. Because the global RAM supports instruction-fetch, it also supports function sharing. By default, each core also has its own stack located in the local RAM.