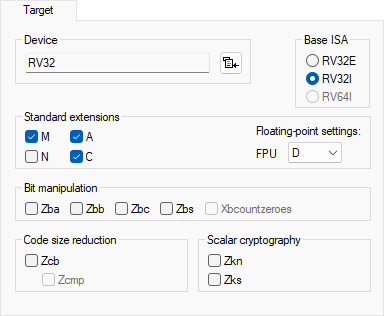

Target

The Target page contains options for the base Instruction Set Architecture (ISA) and extensions for IAR Embedded Workbench for RISC-V.

Device

The device your are using. The choice of device will automatically determine the default linker configuration file and C-SPY® device description file. For information about how to override the default files, see Config and the C-SPY Debugging documentation.

Base ISA

Selects which base ISA to generate code for. Choose between:

- RV32E

Generates code for RV32E.

- RV32I

Generates code for RV32I.

- RV64I

Generates code for RV64I.

Standard extensions

Selects which standard RISC-V extensions to generate code for. For information about the available standard extensions, see Supported RISC-V devices.

Floating-point settings

Selects which standard RISC-V floating-point extension to generate code for. Choose between:

- FPU None

Generates code without support for any of the standard extensions for FPU.

- FPU F

Generates code with support for the Single-Precision Floating-Point extension (F).

- FPU D

Generates code with support for the Double-Precision Floating-Point extension (D).

- FPU Zfinx

Generates code with support for the single-precision floating-point instructions that operate on the integer (x) registers (Zfinx).

- FPU Zdinx

Generates code with support for the double-precision floating-point instructions that operate on the integer (x) registers (Zdinx).

Bit manipulation

Selects which standard RISC-V bit manipulation extensions to generate code for. For information about the available standard extensions for bit manipulation, see ‑‑core.

Code size reduction

Selects which standard RISC-V code size reduction extension to generate code for.

- Zcb

Generates code to add the basic code size assembler instructions.

- Zcmp

Generates code to add instructions to push and pop multiple registers.

For information about the available code size reduction extensions, see ‑‑core.

Scalar cryptography

Selects which standard RISC-V scalar cryptography extension to generate code for.

- Zkn

Generates code with support for the scalar cryptography NIST Algorithms (Zkn).

For information about the available scalar cryptography NIST Algorithms, see ‑‑core.

- Zks

Generates code with support for the scalar cryptography ShangMi Algorithms (Zks).

For information about the available scalar cryptography ShangMi Algorithms, see ‑‑core.